# A Seven Level inverter with Reduced Switch for Various PWM Strategies

K.Meenakshi, C.R.Balamurugan, S.P.Natarajan, T.S.Anandhi

Abstract— This paper presents a three-phase seven-level inverter with RL (Resistive and Inductive) load for various Bipolar Pulse Width Modulation (BPWM) strategies are like Phase Disposition (PD), Phase Opposition and Disposition (POD) PWM, Alternative Phase Opposition and Disposition (APOD) PWM, Carrier Overlapping (CO) PWM and Variable Frequency (VF) PWM sinusoidal reference and trapezoidal reference. The independent work of this paper is equivalence of Total Harmonic Distortion (THD), VRMS and VPEAK for sinusoidal and trapezoidal references. The simulation performance is done through MATLAB /SIMULINK software. COPWM strategy is to perform better as of it provides relatively higher fundamental RMS output voltage.

\_\_\_\_\_

Index Terms- PD, APOD, CO, VF, PWM, Total Harmonic Distortion.

### **1** INTRODUCTION

MultiLevel Inverter (MLI) is relatively used in high Avoltage and high current applications. The desired stepped AC voltage waveform is obtained from several levels of DC voltage. It provides more advantages as compared with conventional two-level inverter which gives lesser switching losses and frequency. The smallest number of voltage/current levels for a multilevel inverter using cascaded inverter. When the number of levels increases eternity, the yield THD overtures zero. This attained number of voltage levels however confined by voltage unbalance problems, circuit setup, packaging restraints, initial and maintenance cost. Behera et al. (2010) introduces multilevel converter fed induction motor drive for industrial and traction drive has less voltage stresses, harmonics, and electromagnetic interferences. Modifications are made in its inbuilt structure.Malinowski et al. (2010) presented, cascaded multilevel inverters which allows one to achieve high quality output voltages and input currents and also outstanding availability due to their intrinsic component redundancy. Lezana et al. (2011) introduced hybrid multi-cell converter in which allows that no losses and high modularity. Floricau et al. (2011) presented a new multilevel converters based on stacked commutation cells with shared power devices. Kangarlu et al. (2012) presented a symmetric multilevel inverter with reduced components based on non-insulated dc voltage sources. Yousedfpoor et al. (2012) proposed an efficient approaching to reduce the harmonic contents of the inverter's output voltage by THD minimization. Rathore et al. (2013) evaluated an optimal pulsewidth modulation of multilevel inverters for low-switchingfrequency control and for harmonic control. Kui Wang et al. (2013) proposed a nine-level inverter which can get over the limitations of traditional neutral-point-clamped and flying capacitor converters. It can be naturally balanced beneath ideal and steady conditions. Ajami et al. (2014) introduced a cascade multi-cell multilevel converter and it has one advantage

that to reduce THD. Buccella et al. (2014) proposed a procedure to eliminate harmonic components from inverter output voltage and, for each harmonic, return the exact boundaries of all valid modulation index intervals. Dayoodnezhad et al. (2014) presents the strategy uses the measured average of the switched phase leg output voltage to adjust the controller hysteresis band as the load back Electro Motive Force (EMF) varies to maintain a near constant phase leg switching frequency.

Hence this paper presents a new seven-level inverter which uses eight power switches. Output voltages are phase voltage VP and line voltage VL can be evaluated by this sevenlevel inverter.

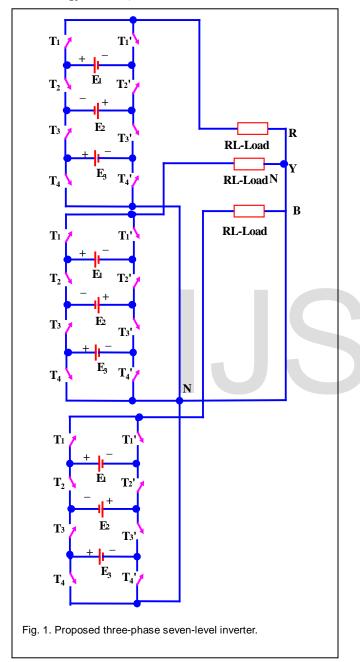

### 2 PROPOSED MULTILEVEL INVERTER

Multilevel inverter is a power electronic device which synthesis an AC voltage/current from desired sinusoidal waveform and actually it divides main DC supply to separate DC voltage sources. The proposed symmetrical multilevel inverter consists of three DC voltage sources (E1, E2 and E3) and eight power semiconductor switches with three-phase Resistive Inductive (RL) load. Three DC voltage sources are, E1=E2=E3=V<sub>dc</sub> and RL- load has  $100\Omega$  and 0.5mH. Proposed MLI needs only eight switches, but for Conventional Cascaded MultiLevel Inverter (CMLI) contains twelve switches to generate symmetrical seven-level inverter. Modes of operation can also be generated by its respective switching patterns.

Bipolar PWM strategies are used to compare the performance measures for both reference waveforms. Trapezoidal is advanced reference waveform while compared with sine reference waveform. Eight switches are T<sub>1</sub>, T<sub>2</sub>, T<sub>3</sub>, T<sub>4</sub>, T<sub>1</sub>', T<sub>2</sub>', T<sub>3</sub>' and T<sub>4</sub>'. When uses of bi-directional switches are Metal Oxide Silicon Field Effect Transistor (MOSFET), Insulated Gate Bipolar Transistor (IGBT) and etc., the losses in switches should be decreased. The seven-level output voltages are +3Idc,  $+2I_{dc}$ ,  $+I_{dc}$ ,  $0I_{dc}$ ,  $-3I_{dc}$ ,  $-I_{dc}$  and  $-I_{dc}$ . This three DC voltage sources produces stepped or staircase waveform from an approximate AC sinusoidal waveform. All performance measures are obtained for both line voltage and phase voltage separately and output voltage waveform also be obtained.

The operation can be explained as: For  $+3I_{dc}$  output switches  $T_1$ ,  $T_3$ ,  $T_2'$  and  $T_4'$  should be in ON position. For +2 $I_{dc}$  output switches  $T_1$ ,  $T_3$ ,  $T_4$  and  $T_2$ ' should be in ON posi-

• S.P.Natarajan, Department of EIE, Annamalai University, India IJSER © 2015 • T.S.Anandhi, Department of EIE, Annamalai University, India

<sup>•</sup> K. Meenakshi, PG student, Department of EEE, Arunai Engineering College, India, +919940727014, meenu.mk7@gmail.com

<sup>•</sup> C.R. Balamurugan, Assistant Professor, Department of EEE, Arunai Engineering College, India, crbalain2010@gmail.com

International Journal of Scientific & Engineering Research, Volume 6, Issue 4, April-2015 ISSN 2229-5518

tion. For +Idc output switches  $T_1$ ,  $T_2'$ ,  $T_3'$  and  $T_4'$  should be in ON position. Same as for 0Idc output switches  $T_1'$ ,  $T_2'$ ,  $T_3'$  and  $T_4'$  should be in ON position. The negative polarity output voltages  $-3I_{dc}$ ,  $-2I_{dc}$  and  $-I_{dc}$  are redundancy for positive polarity output currents. MLI has applications of adjustable speed drives and renewable energy sources (solar cell, Fuel cell, wind energy and etc.).

Figure 1 shows proposed three-phase seven-level inverter with three-phase Y (star) connected resistive inductive load. Therefore, to obtain the total ac voltage produced by the multilevel inverter, there seven distinct ac voltages are added together. The one notices that three distinct dc sources can produce a maximum of seven distinct levels in the output phase voltage of the proposed multilevel inverter. The voltage stress on each switch is decreased. Therefore, the rated voltage and

TABLE 1 SWITCHING TABLE FOR PROPOSED SEVEN-LEVEL INVERTER

| 5.<br>No. |            | Switching States |    |    |                |                |                   |                | Output<br>Voltage |

|-----------|------------|------------------|----|----|----------------|----------------|-------------------|----------------|-------------------|

|           | <b>T</b> 1 | T2               | T; | T4 | $T_1^{\prime}$ | $T_2^{\prime}$ | $\mathbf{T}_{3}'$ | $T_4^{\prime}$ |                   |

| 1         | 1          | 0                | 1  | 0  | 0              | 1              | 0                 | 1              | + 31 de           |

| 2         | 1          | 0                | 1  | 1  | 0              | 1              | 0                 | 0              | +Idc              |

| з         | 1          | 0                | 0  | 0  | 0              | 1              | 1                 | 1              | Ide               |

| 4         | 0          | 0                | 0  | 0  | 1              | 1              | 1                 | 1              | 0                 |

| 5         | 0          | 1                | 1  | 1  | 1              | 0              | 0                 | 0              | -Ide              |

| 6         | 0          | 1                | 0  | 0  | 1              | 0              | 1                 | 1              | -2I <sub>dc</sub> |

| 7         | 0          | 1                | 0  | 1  | 1              | o              | 1                 | 0              | -3I <sub>de</sub> |

consequently the total inverter power could be safely increased by increasing the resistive load value.

Three input dc sources with  $E_1 = E_2 = E_3 = 50$  V are used. The switching table so obtained is shown in Table 1, which shows that switches  $T_2$ ,  $T_2'$ ,  $T_3$  and  $T_3'$  operate at a fundamental frequency of 50 Hz while switches  $T_1$ ,  $T_1'$ ,  $T_3$ , and  $T_3'$ operate at a frequency 2 kHz. Thus, low-voltage-rated switches operate at high frequency and incur more switching losses, while high-voltage rated switches operate at fundamental frequency and incur more conduction losses. In this manner, the total losses among the switches get distributed. Switching losses are very directly proportional to the switching frequency. This paper evaluates THD, I<sub>RMS</sub> and I<sub>PEAK</sub> for both line voltage and phase voltage. Comparison of THD and RMS fundamental output voltage for sine and trapezoidal references can also be determined through FFT analysis.

### **3 SWITCHING SCHEME**

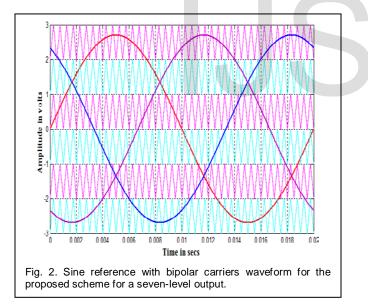

High-switching-frequency modulation methods like multicarrier bipolar PWM and space vector modulation techniques have been used for MLI modulation control. The proposed topology can be modulated with any one of these methods with suitable adjustment. In the present work, the multicarrier bipolar PWM scheme is used. In a multicarrier bipolar PWM scheme, carrier signals are compared with the reference signal, and the pulses obtained are used for switching of devices corresponding to respective voltage levels. In the proposed topology, one switch may contribute for synthesis of more than one level at output terminals.

The modulating/reference wave of multilevel carrier based PWM strategies can be sinusoidal PWM signal. The reference wave is concerned for CFD including frequency, amplitude and phase angle of the reference wave. The following strategies are employed in this study. This switching table will lead to fundamental switching of  $T_2$ ,  $T_2'$ ,  $T_3$  and  $T_3'$  which bear voltage stress of  $2V_{dc}$  each as compared to the remaining switches which bear voltage stress of Vdc each. This treatment

can, however, be extended for higher level inverters. In this various Bipolar PWM techniques but for only one sample technique Bipolar Phase Disposition (BPD) PWM is used. Because this technique generate reduced total harmonic distortion.

Bipolar multicarrier techniques with sine reference are as given: In Phase disposition technique, all the carriers are in phase with each other. For an m-level inverter using bipolar multicarrier technique, (m-1) carriers with the same frequency fc and same peak-to-peak amplitude Ac are used. The reference waveform has amplitude Am and frequency fm and it is ended at zero level. The three-phase sine reference wave is continuously compared with each of the carrier signal. If the reference wave is more than a carrier signal, then the active devices corresponding to that carrier are switched on. Otherwise, the devices would be switched off. The frequency ratio mf is defined in the PWM strategy as follows:

$$m_f = \frac{f_c}{f_m}$$

The amplitude modulation index ma of this method is

$$m_a = \frac{A_m}{n^*A_c}$$

Figure 2 shows the multicarrier arrangement for PDPWM method for  $m_a = 0.9$  and  $m_f = 40$ .

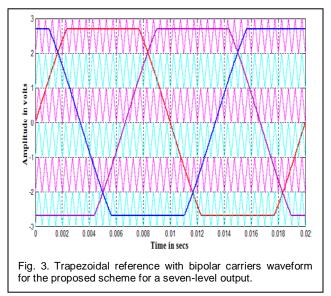

Same as of amplitude modulation index  $m_a$  and frequency modulation index  $m_f$  for trapezoidal reference with bipolar PDPWM technique. This technique is advanced technique while compared with sinusoidal reference. It gives lesser harmonic distortion, higher fundamental RMS output current, less DC component and higher peak current (fundamental). Figure 3 shows the multicarrier arrangement for PDPWM method for  $m_a = 0.9$  and  $m_f = 40$ .

#### 4 SIMULATION RESULTS

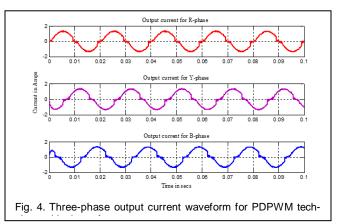

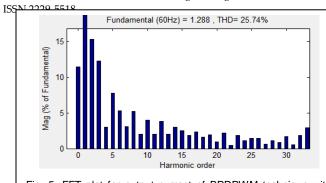

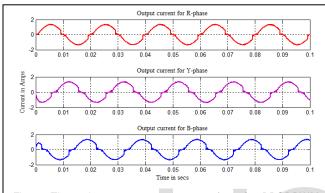

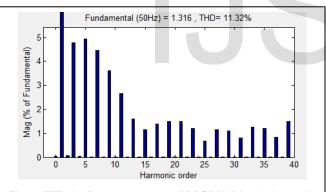

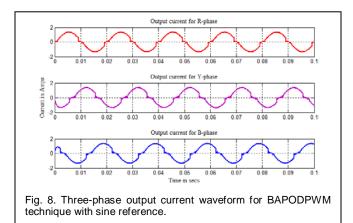

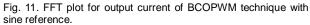

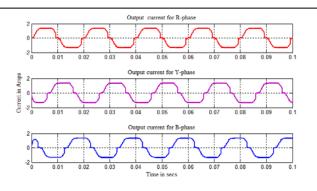

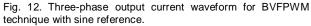

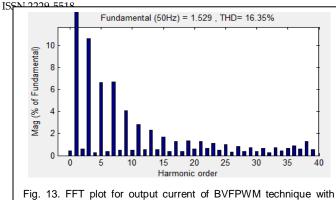

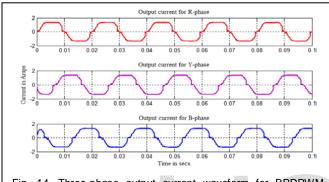

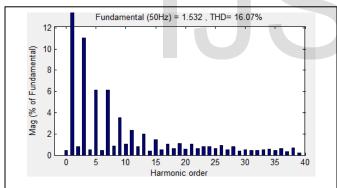

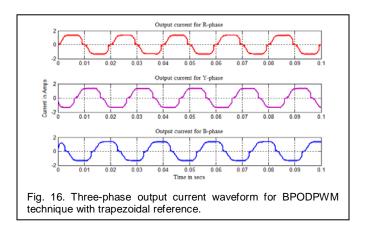

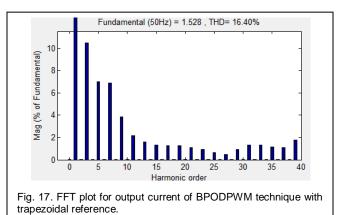

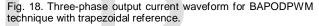

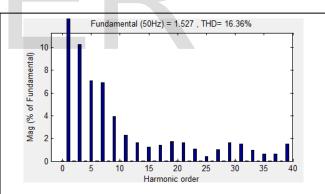

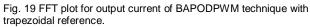

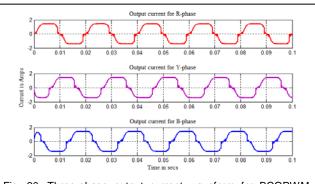

The three-phase cascade seven-level inverter can be modeled in SIMULINK model by using power system block set. Switching signals for Cascaded Multi Level Inverter (CMLI) are developed using BPWM techniques but for only one sample technique BPDPWM is used. The power balancing among input dc sources is important so that all dc sources have equal lifetimes. Power balancing is also crucial when the DC sources are renewable sources such as PV cells. The simulation is performed for different values of ma ranging from 0.7-1. The corresponding %THD values and IRMS of fundamental and peak amplitude current IPEAK of inverter output for same modulation indices corresponding of FFT plots and they are shown in below tables. Below figures shows the simulated output current waveforms for a CMLI and corresponding FFT plots but for only one sample value of ma = 0.9. Tables 2 - 7 obtain the performance measures such as %THD, I<sub>RMS</sub>, I<sub>PEAK</sub> and DC component. Figures 4 - 23 shows the three-phase output current (line) waveforms for sine and trapezoidal references and its respective FFT plots.

#### 4.1 Simulation Results for Sinusoidal Reference PWM

Fig. 5. FFT plot for output current of BPDPWM technique with sine reference.

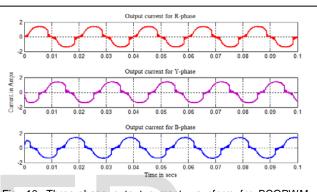

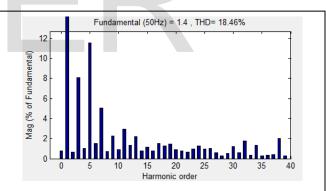

Fig. 6. Three-phase output current waveform for BPODPWM technique with sine reference.

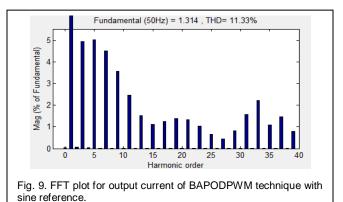

Fig. 7. FFT plot for output current of BPODPWM technique with sine reference.

IJSER © 2015 http://www.ijser.org

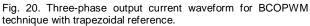

Fig. 14. Three-phase output current waveform for BPDPWM technique with trapezoidal reference.

Fig. 15. FFT plot for output current of BPDPWM technique with trapezoidal reference.

Output current for R-phase Output current for R-phase Output current for Y-phase Output current for Y-phase Output current for Y-phase Output current for B-phase O

IJSER © 2015 http://www.ijser.org

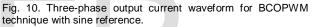

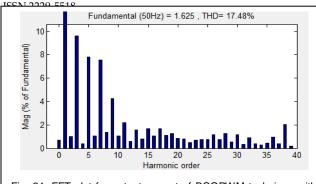

Fig. 21. FFT plot for output current of BCOPWM technique with trapezoidal reference.

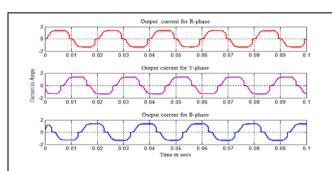

Fig. 22. Three-phase output current waveform for BVFPWM technique with trapezoidal reference.

TABLE 2 %THD FOR DIFFERENT MODULATION INDICES WITH SINE REFERENCE

| m,  | PD    | POD   | APOD  | 00    | VF    |

|-----|-------|-------|-------|-------|-------|

| 1   | 12    | 10.94 | 10.9  | 15.49 | 1293  |

| 0.9 | 12.56 | 11.32 | 11.33 | 18.46 | 14%   |

| 0.8 | 15.52 | 16.73 | 16.78 | 22.24 | 168   |

| 07  | 18.87 | 17.55 | 17.5  | 26.74 | 20.89 |

TABLE 3

I<sub>RMS</sub> FOR DIFFERENT MODULATION INDICES WITH SINE

REFERENCE

| ma  | PD     | POD    | APOD   | со     | VF     |

|-----|--------|--------|--------|--------|--------|

| 1   | 1.028  | 1.034  | 1.033  | 1.079  | 1.026  |

| 0.9 | 0.925  | 0.9307 | 0.9294 | 0.9899 | 0.9167 |

| 0.8 | 0.8121 | 0.8068 | 0.8069 | 0.8927 | 0.8083 |

| 0.7 | 0.6985 | 0.7037 | 0.7047 | 0.7764 | 0.6931 |

| TABLE 4                                                                  |

|--------------------------------------------------------------------------|

| $I_{\mbox{\scriptsize PEAK}}$ for Different Modulation Indices with Sine |

| Reference                                                                |

| ma  | PD     | POD    | APOD   | со    | VF      |

|-----|--------|--------|--------|-------|---------|

| 1   | 1.454  | 1.462  | 1.461  | 1.526 | 1.45    |

| 0.9 | 1.308  | 1.316  | 1.314  | 14    | 1.296   |

| 0.8 | 1.148  | 1.141  | 1.141  | 1.26  | 1 1 4 3 |

| 0.7 | 0.9879 | 0.9951 | 0.9965 | 1.098 | 0.9802  |

TABLE 5 %THD FOR DIFFERENT MODULATION INDICES WITH TRAPEZOIDAL REFERENCE

| ma  | PD    | FOD   | APOD  | 00    | VF    |

|-----|-------|-------|-------|-------|-------|

| ma  | TD.   | 100   | AIOD  |       | vr    |

| 1   | 15.48 | 15.16 | 15.26 | 17.18 | 15.70 |

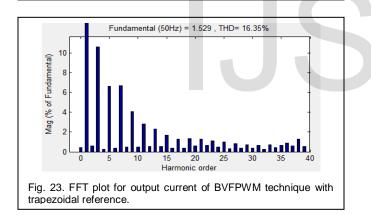

| 0.9 | 16.07 | 16.40 | 16.36 | 17.48 | 16.35 |

| 0.8 | 16.37 | 16.52 | 16.62 | 17.40 | 16.56 |

| 0.7 | 17.02 | 16.85 | 16.75 | 18.23 | 17.61 |

International Journal of Scientific & Engineering Research, Volume 6, Issue 4, April-2015 ISSN 2229-5518

TABLE 6

I<sub>RMS</sub> FOR DIFFERENT MODULATION INDICES WITH TRAPEZOIDAL

REFERENCE

| ma  | PD     | POD    | APOD   | со    | VF     |

|-----|--------|--------|--------|-------|--------|

| 1   | 1.212  | 1.214  | 1.215  | 1.215 | 1.207  |

| 0.9 | 1.083  | 1.081  | 1.08   | 1149  | 1.081  |

| 0.8 | 0.9695 | 0.9649 | 0.9655 | 1.095 | 0.9683 |

| 0.7 | 0.8395 | 0.8442 | 0.8438 | 1.024 | 0.8363 |

TABLE 7 IPEAK FOR DIFFERENT MODULATION INDICES WITH TRAPEZOIDAL REFERENCE

| ma  | PD     | POD    | APOD   | со    | VF     |

|-----|--------|--------|--------|-------|--------|

| 1   | 1.212  | 1.214  | 1.215  | 1.215 | 1.207  |

| 0.9 | 1.083  | 1.081  | 1.08   | 1.149 | 1.051  |

| 0.8 | 0.9695 | 0.9649 | 0.9655 | 1.095 | 0.9683 |

| 0.7 | 0.8395 | 0.8442 | 0.8438 | 1.024 | 0.8363 |

## 6 CONCLUSION

The 7-level CMLI using eight switches is successfully introduced while the simulation done by MATLAB/ SIMULINK and observed a clear stepped 7-level waveform. Mainly found that the APODPWM strategy has lesser %THD while compared with all other PWM strategies for both references. The COPWM strategy is produce higher fundamental RMS output current. The new design is simple in its outlook and only few components were used. The novel 7-level multilevel inverter has lower THD compared to conventional symmetric and asymmetric topologies.

## REFERENCES

- R.K.Behera, S.P. Das, "Multilevel converter fed induction motor drive for industrial and traction drive", IEEE Potentials, vol. 29, no. 5, pp. 28 - 32, 2010.

- [2] Malinowski, M., Gopakumar, K., Rodriguez, J., Perez, M.A., "A survey on cascaded multilevel inverters", IEEE Trans. Ind. Electron., vol. 57, no. 7, pp. 2197 2206, 2010.

- [3] Lezana, P., Aceiton, R., "Hybrid multicell converter: Topology and Modulation", IEEE Trans. Ind. Electron., vol. 58, no. 9, pp. 2605 – 2612, 2011.

- [4] Floricau, D., Richardeau, F., "New multilevel converters based on stacked commutation cells with shared power devices", IEEE Trans. Ind. Electron., vol. 58, no. 10, pp. 4675 - 4682, 2011.

- [5] Kangarlu, M.F., Babaei, E., Laali, S., "Symmetric multilevel inverter with reduced components based on non-insulated dc voltage sources," IET Power Electron., 2012, vol. 5, no. 5, pp. 571–581.

- [6] Yousedfpoor, N., Fathi, S.H., Farokhnia, N., Abyaneh, H.A., "THD Minimization Applied Directly on the Line-to-Line Voltage of Multilevel Inverters," IEEE Trans. Industrial Electron, vol. 59, no. 1, pp. 373 - 380, 2012.

- [7] Rathore, R., Holtz, H., Boller, T., "Generalized optimal pulsewidth modulation of multilevel inverters for low-switching-frequency control of medium-voltage high-power industrial AC drives", IEEE Trans. Ind. Electron., vol. 60, no. 10, pp. 4215 – 4224, 2013.

- [8] Kui Wang, Zedong Zheng, Yongdong Li, Kean Liu, Jing Shang, "Neutral-point potential balancing of a five-level active neutralpoint-clamped inverter", IEEE Trans. Ind. Electron., vol. 60, no. 5, pp. 1907 – 1918, 2013.

- [9] Ajami, A., Reza jannti oskuee, M., Toopchi khosroshahi, M., Mokhberdoran, A., "Cascade-multi-cell multilevel converter with reduced number of switches", IET Power Electron., vol. 7, no. 3, pp. 552 – 558, 2014.

- [10] Buccella, C., Cecati, C., Cimoroni, M.G., Razi, K., "Analytical method for pattern generation in five-level cascaded H-bridge inverter using selective harmonic elimination", IEEE Trans. Ind. Electron., vol. 61, no. 11, pp. 5811 – 5819, 2014.

- [11] Dayoodnezhad, R., Holmes, D., McGrath, B.P., "A novel three-phase hysteresis current regulation strategy for three-phase three-level inverters", IEEE Trans. Power Electron., vol. 29, no. 11, pp. 6100 – 6109, 2014.